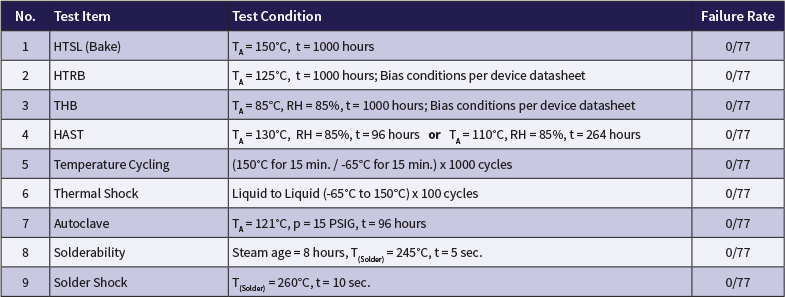

Reliability Tests

Central Semiconductor performs extensive reliability stress testing on a variety of products from our product portfolio. This data is collected in addition to Central's standard qualification test data for any new or changed product.

Typical Results:

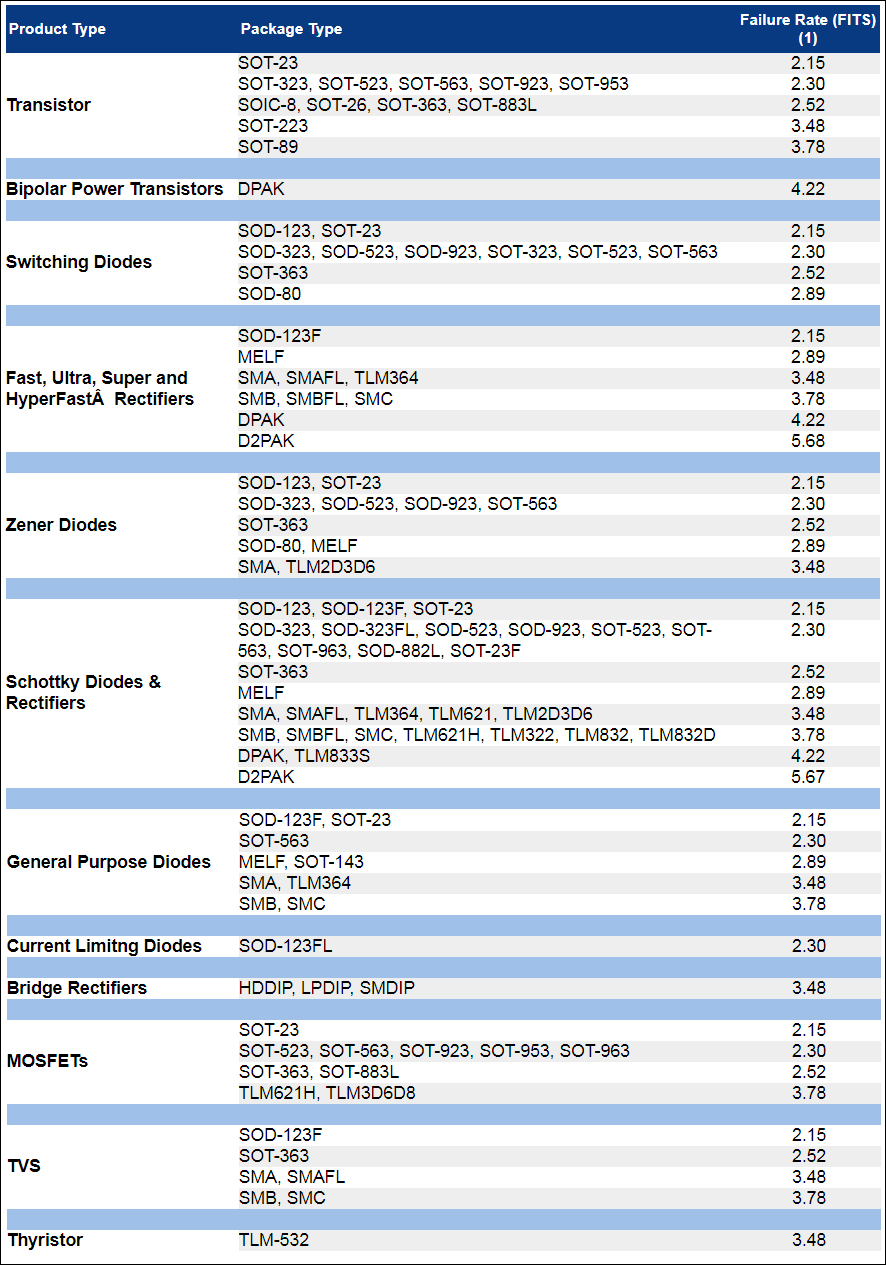

Reliability - FIT Rate (HTRB Life)

Data noted herein is based on standard FIT rate calculations as detailed below.

FIT rate calculations:

(1) 60% Confidence Level. Accelerated testing.

Formulas

The failure rate calculation based on a single life test is as follows:

λ = Failure Rate

TDH = Total Device Hours

AF= Acceleration Factor

The Accelleration Factor is calculated as follows:

Ea = Thermal Activation Energy

k =Boltzmann's Constant (8.63 x 10-5 eV)/K

Tuse= Use Temperature (°C + 273)

Tstress = Life test stress temperature (°C + 273)

The comprehensive failure rate is calculated as follow:

β = Number of distinct possible failure mechanisms

k= Number of life tests combined

xi = Number of failures for a given mechanism (1 = 1, 2, ... B)

TDHj = Total device hours of test time for life testj (j = 1, 2,... k)

AFij = Acceleration factor for appropriate failure mechanism (i = 1, 2,... k)

M = X² (∝ , 2r +2) / 2

(where X² = chi square factor for 2r +2 degrees of freedom, r = total number of failures, ∝ = risk associated with CL between 0 and 1)

Package Reliability Summaries

Reliability Summaries for surface mount and through-hole package types can be found in the "Package Reliability" column of the tables below.