# **Boosting the Current Limit of Current Limiting Diodes**

As seen in ECN

by Sze Chin, Central Semiconductor Corp

#### Introduction

The current limiting diode (CLD) or current regulating diode (CRD), despite its simplicity and distinct advantage over a conventional transistorized current source, has limited use. One

reason is that presently available CLD's can provide current regulation only up to 15mA maximum, and in terms of power, only 1 watt maximum. Hence, the usefulness of the CLDs is limited to low power applications such as telephone line circuit modules, handheld devices and single IC chips or small areas of a PC board. However, the bulk of electronic applications involve current levels much higher than 15 mA and the same may be said of the power levels. Conventionally, by adding the CLDs in parallel, the limiting current may be doubled, tripled, and multiplied. However, it would be cumbersome and impractical by just adding the CLDs to attain high current levels. For example, it is not uncommon to require a current limit protection at 1 amp or higher at the conventional PC card or system module level. It would not make any practical sense to use 66 CLDs in parallel to attain 1 amp or 100 CLDs to attain 1.5 Amp. Therefore, the need for a practical solution to achieve high current limit is evident.

Presented henceforth is a simplified description of the practical circuit design technique to boost the current limit by utilizing the current gain of a transistor and applying basic circuit theory.

# **Practical Current Booster Circuit Technique.**

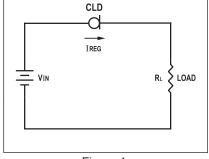

Conventional Circuit Using CLD: A convenentional circuit using a CLD is shown in Figure 1. In this circuit, the current limiting diode CLD regulates thr current  $I_{REG}$  against the change in input voltage  $V_{IN}$  or Load  $R_L$ . If the input voltage  $V_{IN}$  increases, the CLD absorbs the voltage increase and regulates the current  $I_{REG}$  and hence maintains a constant voltage across the load  $R_L$ . Likewise if the load changes,  $I_{REG}$  remains

constant and the CLD absorbs change in voltage across the load. This circuit has limitations in both current and power dissipation. The highest current rating of presently available CLDs is 15 mA and the highest power rating is 1 Watt.

Figure 1.

#### Current Boosting Circuit Technique:

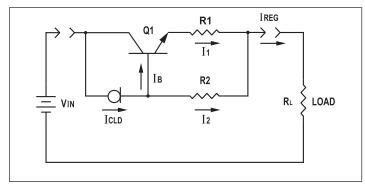

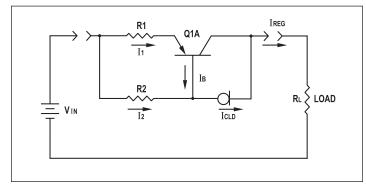

The current boosting circuit is shown in Figure 2A and 2B. In this circuit, the transistor  $Q_1$  (NPN), or  $Q_{1A}$  (PNP) amplifies the CLDs current and the ratio of resistor  $R_1$  and resistor  $R_2$  determines the current. Figure 2A shows the current booster with an NPN transistor and Figure 2B with a PNP transistor. The principle of operation of the two circuits is basically the same except for the polarity of current.

## **Analysis of Booster Circuit**

Through the following circuit analysis, the principle of operation may be readily understood. Assume the transistor Q1 is ideal; that its current gain  $\beta$  is infinite and its input  $V_{BE}$  offset voltage is zero. As  $\beta=\infty$ ,  $I_B=0$  and all the CLD's current flows through  $R_2$ . By summing the voltage loop through the base to emitter, and resistor  $R_1$  and  $R_2$ , we have

$$I_1 R_1 = I_2 R_2$$

$I_1 = I_2 R_2/R_1$

Since  $I_{REG} = I_1 + I_2$

The current gain

$$G_{I} = \frac{I_{REG}/I_{CLD}}{G_{I}}$$

$$G_{I} = \frac{I_{1} + I_{2}}{I_{2}}$$

$$G_{I} = \underbrace{I_{2} \ R_{2}/R_{1} + I_{2}}_{I_{2}}$$

$$G_1 = R_2/R_1 + 1$$

If  $R_2/R_1 >> 1$ , then  $G_1 = R_2/R_1$ --(I)

If the transistor b had been considered above, the current gain would be:

$$G_{I} = \frac{R_{2} \dots(2)}{R_{2}/\beta + R_{1}}$$

# **Practical Considerations in Implementation.**

A practical circuit is one that is implemented with due consideration on the effect of its components characteristics

Figure 2A. Current Booster with NPN transistor

Figure 2B. Current Booster with PNP transistor

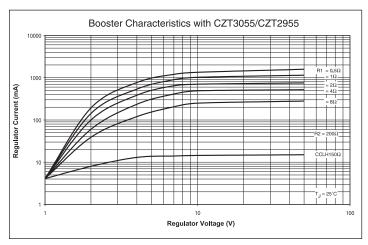

Figure 3. Regulator Voltage (V).

over its performance. Comprising the booster circuit are the transistor, current limiting diode (CLD), and two resistors. Characteristics of the transistor affecting circuit performance are its current and capacities, B-E voltage offset and current gain. With the CLD, it is the regulating current level. As to the two resistors it is their values and tolerance. Also the components characteristics change with temperature, therefore, the temperature effect should be accounted for.

## **Exemplary Experimental Result.**

For illustration, the complementary NPN CZT3055 and PNP CZT2955 are implemented in the booster circuit with the amplifying resistors R2 set at  $200\Omega$ , and R1 at 0.5, 1, 2, 4 and  $8\Omega$ . The experimental result is presented on Figure 3 as regulator current versus regulator voltage. It can be seen that at  $R_1$  =  $0.5\Omega$ ,  $I_{REG}$  is 1.5 Amps. This is 100 times greater than the CLD CCLH150's 15 mA. For comparison, the  $I_{REG}$  versus  $V_{REG}$  characteristics of the CLD is also shown on Figure 3. Since the booster current increases with the transistors current gain  $\beta$ , the regulator would be greater than 1.5 Amps had a higher  $\beta$  transistor been used, such as the Darlington transistor.

### **Conclusion**

Based on sound basic circuit theory and experimental validation, a simple high current regulating or limiting device is now feasible. Composing of only one transistor, one current limiting diode (CLD), and two resistors, this device can boost the CLD's current to much higher levels limited only by the current capacity and current gain of the transistor used. Likewise, it can boost the power to a much higher level limited only by the transistor's power rating. The significance of this current boosting device is self-evident; since it can easily replace at least 100 high current CLD's functionally.

The same current amplifying technique as presented is not limited only in current limiting application, but also in any other application requiring current amplification.

#### About the author

Sze Chin is Senior Applications Engineer for Central Semiconductor Corp. in Hauppauge, NY. He holds a B.S.E.E. from Rensselaer Polytechnique Institute and has been designing analog and digital circuits for over 30 years for such companies as Grumman, NCR, IBM and General Dynamics. He can be contacted at (631) 435-1110 or schin@centralsemi.com.